TM 11-5895-856-34-1/EE640-CA-MMI-010/ E154 CPU/TO 31W2-2T-122-1

The LPC operates in one of two states: active or

2-21. Random Access Storage Controller

inactive. The active state is entered whenever a device

command to enable data transfer is detected. In this

The random access storage controller (RASC) provides

state, data is transferred from the computer to the line

the interface between a random access storage (RAS)

printer in response to a data request from the line

unit and the two processors. The RASC can access any

printer.

A command to determine status will be

given sector and track address on any selected RAS in

acknowledged in the active state; however, a command

a maximum of 34 milliseconds. Each track is divided

to perform the self-test will not be accepted. The

into 90 data sectors and one maintenance sector. A

inactive state is entered on power up, receipt of a

sector contains 21 data words and a longitudinal

master reset or device stop command, and on detection

redundancy check word, each consisting of 32 data bits

of an end-of-block. A command to determine status will

plus one parity bit. The RASC has an average transfer

be acknowledged in the inactive state as well as in the

rate of 57,000 33-bit words per second. The RASC is

active state. A command to perform self-test will also

connected to the computer via an IOE interface.

be acknowledged in the inactive state.

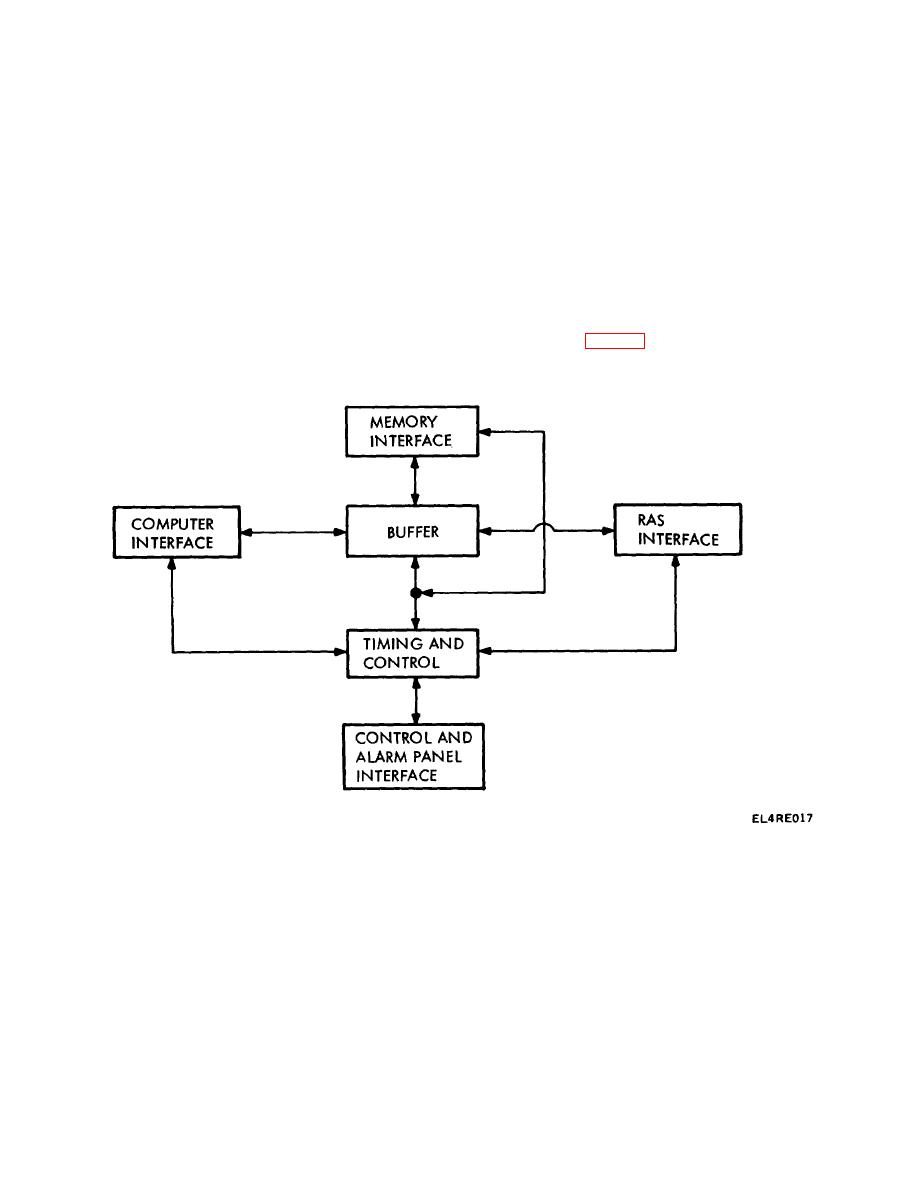

Functional organization of the RASC is shown in the

block diagram (fig. 2-5).

Figure 2-5. RASC Block Diagram.

A dual-channel switch allows access to the RASC by

and checked for each sector of the disc. An on-line

either or two computers on a switched basis. The I/O

cycle test capability is provided whereby the RASC is

module connected between the RASC and RAS

commanded to read the contents of an entire disc,

monitors the ready status of each of the discs and

checking all data for parity and cyclic check errors,

controls and data paths between the RASC and RAS.

without transferring any data to the computer. The

All command codes and data from the computer are

RASC receives commands either from the processor or

checked by the RASC for correct parity. Each word

directly from memory. These commands are divided so

read from the RAS includes a parity bit which is checked

that the RASC control type commands originate in the

and each word written includes a parity bit generated by

processor while the operational type commands are

the RASC. In addition, a cyclic check-word is written

2-10

Previous Page

Previous Page