TM 11-5895-856-34-1/EE640-CA-MMI-010/ E154 CPU/TO 31W2-2T-122-1

two device commands: indicated data received without

2-initiate information transfer. Upon receipt of a start

error and indicated error detected during input. Upon

command, the PPI will execute an interrupt to the off-

receiving the device command, the PPI will modify the

line CPU. The status byte will be transmitted via the

status byte by clearing the start command and executing

interrupt. The PPI then waits until an acknowledge

an interrupt to the on-line CPU.

The data error

device command is received from the off-line CPU

command will cause the parity error bit for the off-line

before initiating the automatic transfer from the on-line

CPU to be set in the status byte. Upon receiving the

CPU (auto output) to the off-line CPU (auto input). The

interrupt, the on-line CPU will issue a release command

data transfer at this point is limited up to 50,000 words-

to give up control of the PPI or a new start command to

per-second by a free-running timer. The PPI will

continue operation. On power-up and upon receipt of a

continue transferring data words via the automatic

master reset or device stop command from either CPU,

functions until terminated by the on-line CPU. At this

the PPI control logic will be initialized.

point, the PPI will execute an interrupt to the off-line

CPU. The off-line CPU then issues one of the following

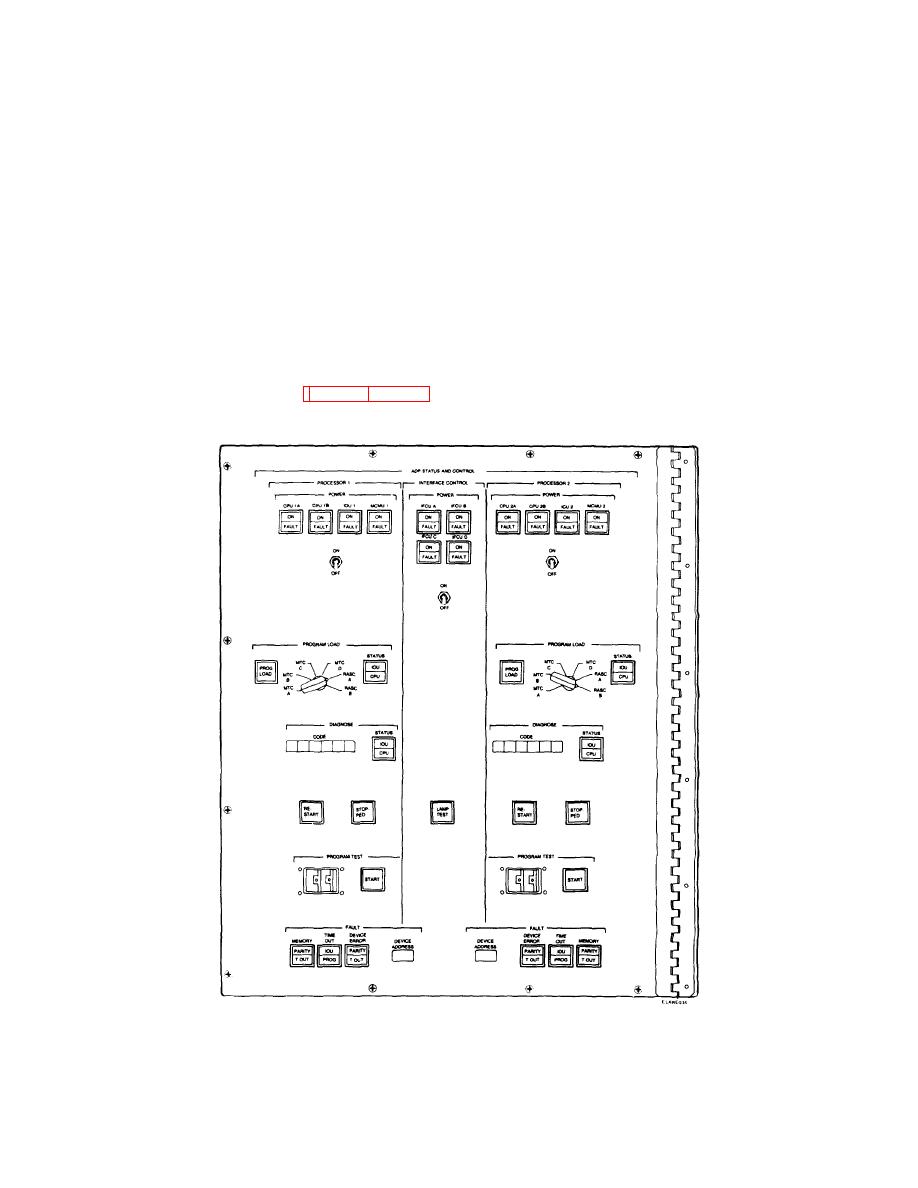

Section VI. ADP STATUS AND CONTROL PANEL

2-23. General

for status monitoring and functional control of the

The ADP status and control panels (figs. 2-7 and 2-8)

processors.

contains the controls and indicators necessary

Figure 2-7. ADP Status and Control Panel (Message Switch).

2-12

Previous Page

Previous Page